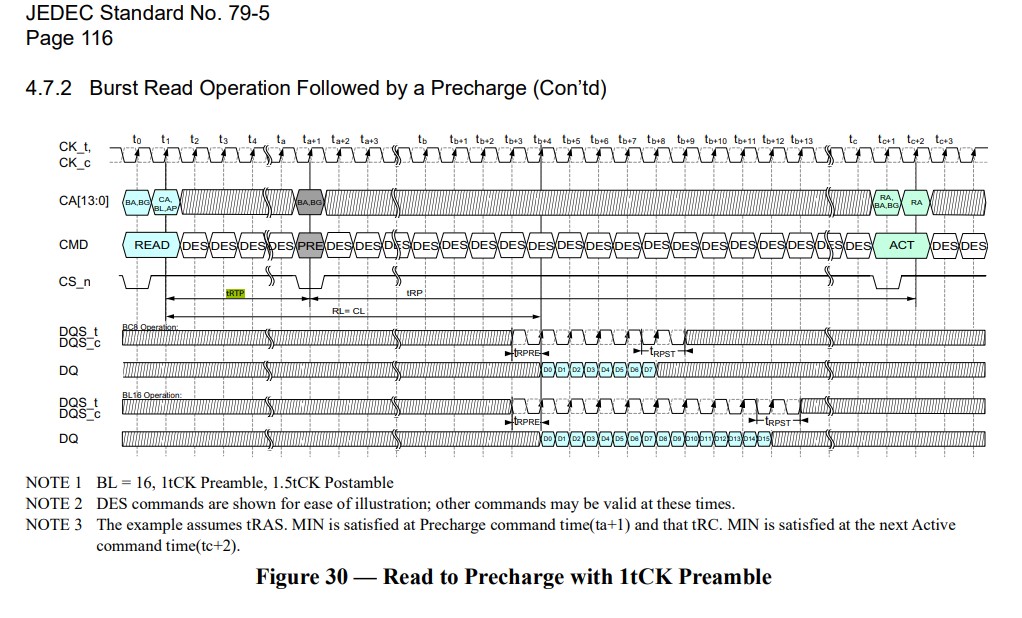

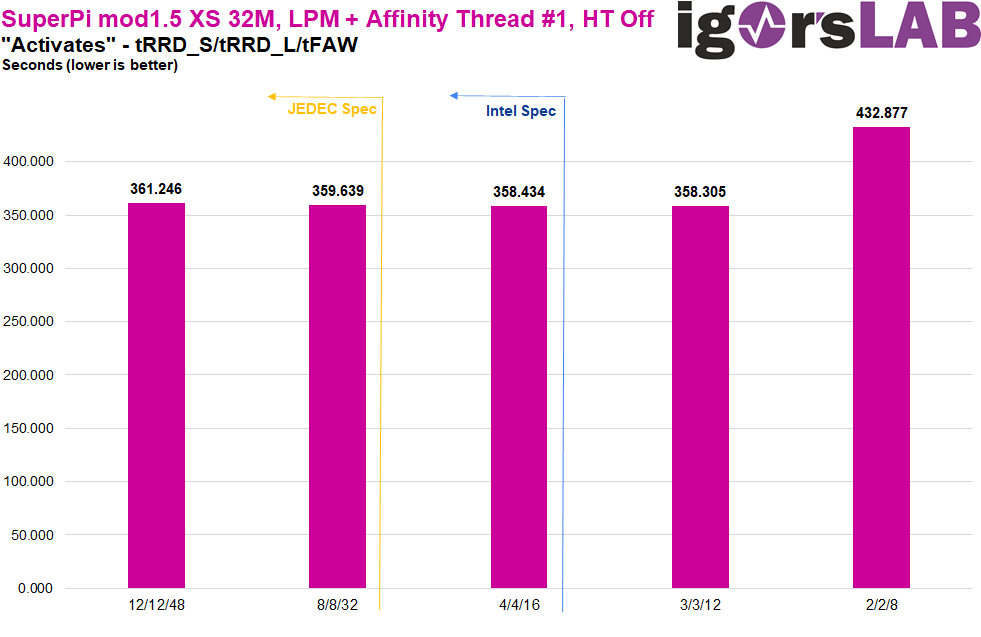

JEDEC vs. Intel DDR5 specs – timings tRRD_S, tRRD_L, tFAW and tRTP in benchmark tests with Alder Lake | Page 4 | igor'sLAB

JEDEC vs. Intel DDR5 specs – timings tRRD_S, tRRD_L, tFAW and tRTP in benchmark tests with Alder Lake | Page 6 | igor'sLAB

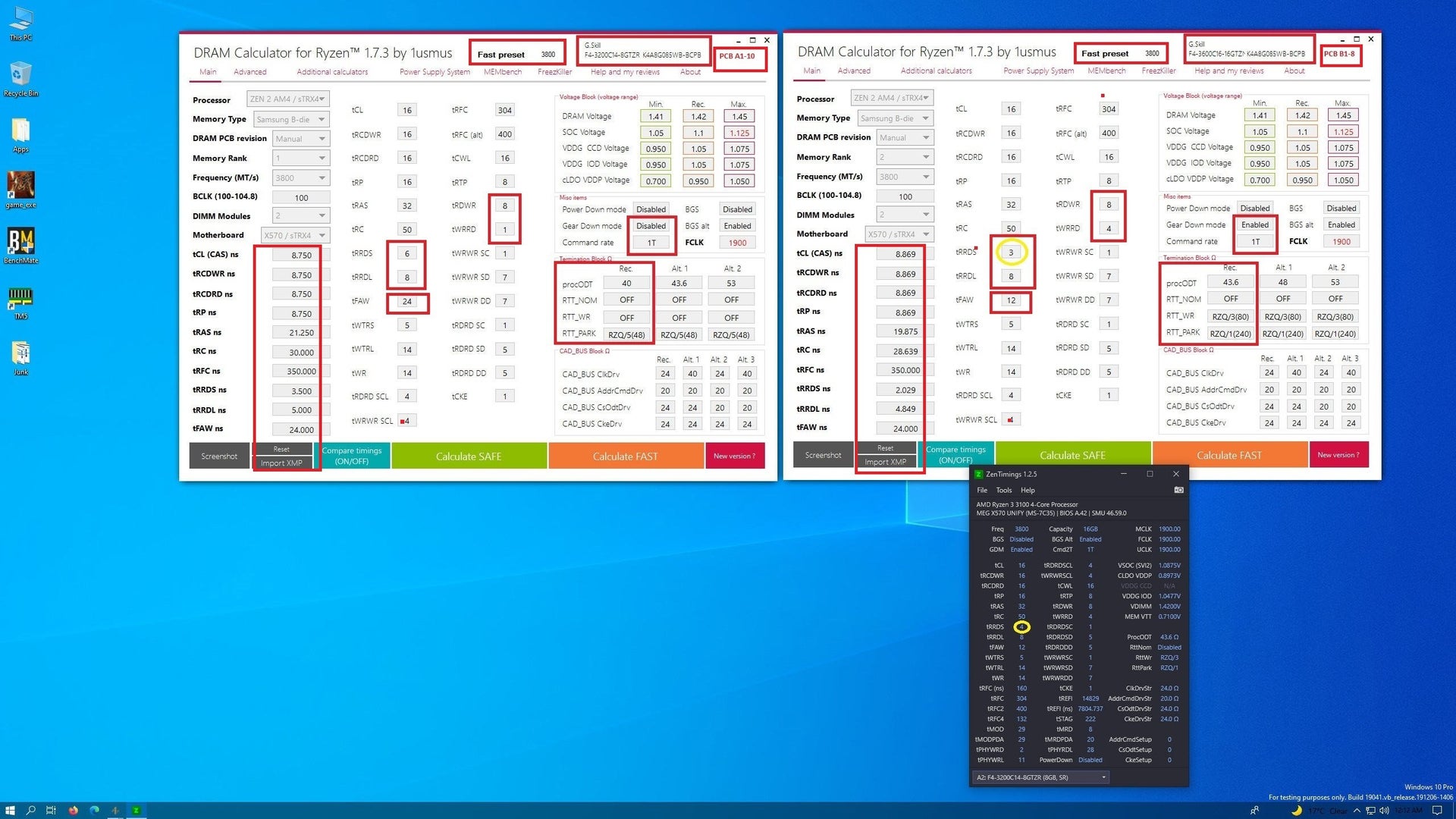

Tighter timings on new RAM = Solved Stability Issues.... Does Ryzen Prefer (3900x) low TFaw and TWr memory timings on Samsung B-Die.. really Bizzare behaviour! : r/Amd

Can I use 3600MHz CL16 DR (3800/1900) RAM Calculator Timings on my 3200MHz CL14 SR without any negative effect? | Overclock.net

What Are Memory Timings? CAS Latency, tRCD, tRP, & tRAS (Pt 1) | GamersNexus - Gaming PC Builds & Hardware Benchmarks

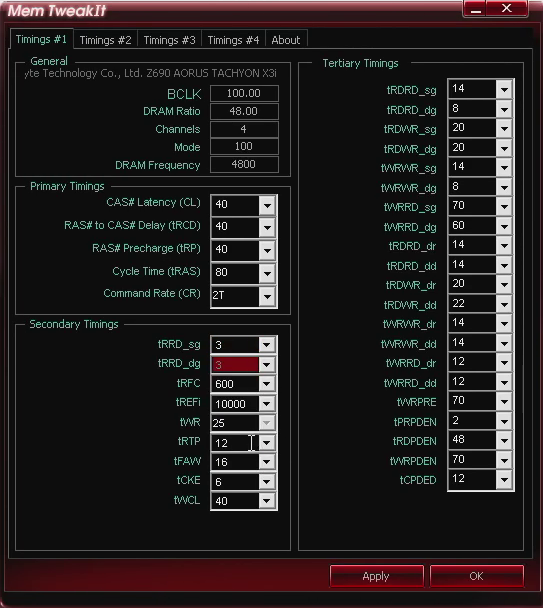

Guide] - RAM Timings und deren Einfluss auf Spiele und Anwendungen (AMD) - Update 23.05.2020 | Hardwareluxx

Third time my RAM OC became unstable within several weeks of completing stability tests. DRAM voltage is set to 1.35V. What could be the cause? | Overclock.net

![SOLVED] - 3600 Mhz ram works at 3200 Mhz even with XMP enabled ? | Tom's Hardware Forum SOLVED] - 3600 Mhz ram works at 3200 Mhz even with XMP enabled ? | Tom's Hardware Forum](https://s6.uupload.ir/files/16479437267054611606110118463592_96y.jpg)

![Ryzen instability [solved] - #17 by catsay - Hardware - Level1Techs Forums Ryzen instability [solved] - #17 by catsay - Hardware - Level1Techs Forums](https://forum.level1techs.com/uploads/default/original/3X/9/a/9ac14a8405b0a047185ad13ed86cee00cc270937.jpg)

![Ryzen instability [solved] - #17 by catsay - Hardware - Level1Techs Forums Ryzen instability [solved] - #17 by catsay - Hardware - Level1Techs Forums](https://forum.level1techs.com/uploads/default/original/3X/8/e/8e097eac477d8c89f6c9fce968ad15574f81f137.jpg)

![3800x + Corsair 32GB Kit Latency? | [H]ard|Forum 3800x + Corsair 32GB Kit Latency? | [H]ard|Forum](https://cdn.hardforum.com/data/attachment-files/2021/08/486277_Zen-Timings-Screenshot.png)